#### Digital ASIC Fabrication SDMAY24-21

Haris Khan Jonathan Hess Samuel Heikens Yu Wei Tan

Client & Advisor: Dr. Henry Duwe

#### **Project Vision**

#### **Problem Statement:**

- Digital ASIC fabrication is a valuable skill, but it is not in the undergraduate curriculum

- Traditional guitar pedals are incapable of having multiple effects

#### Objective:

- Learn EFabless tools & ASIC fabrication flow

- Develop an ASIC for guitar pedals that allow multiple effects

- Develop documentation to pass on knowledge to future teams

## **Project Purpose**

- Reduced need for multiple guitar pedals

- Standardized pedal for Studio Artists

- Provide more knowledge and resources to open source pool

- Create project that can be worked on by future students with CPRE 288 experience without knowledge of ASIC fabrication

## **Project Scope**

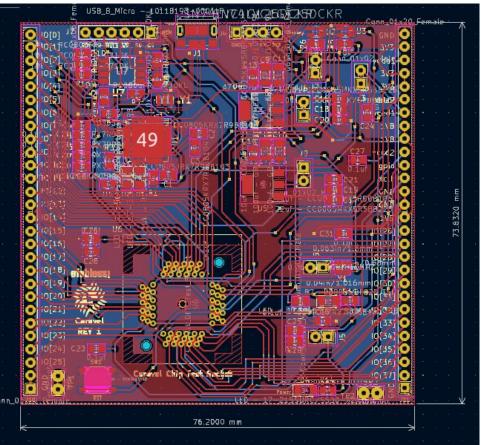

#### • Design and send to EFabless chip design

- Setup workspace in docker

- Design modules in verilog

- $\circ \quad \text{Test Individual Modules} \\$

- Compile Verilog Modules

- Test Compiled Verilog Modules

- Select Off Chip components like data converters and memory

- Generate Layout

- Send to EFabless

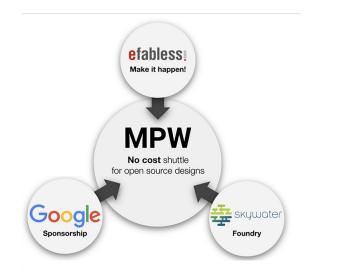

#### **ASIC Fabrication**

#### Who:

- EFabless Open MPW Program

#### What:

ASIC Fabrication at zero cost to developers

Why:

- Open-source platform

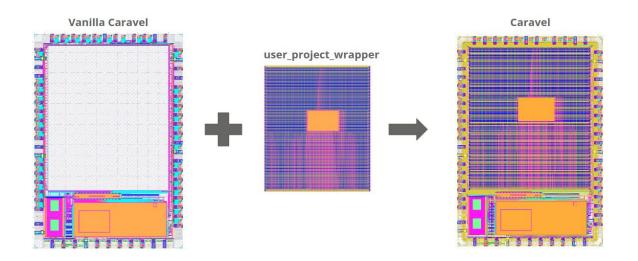

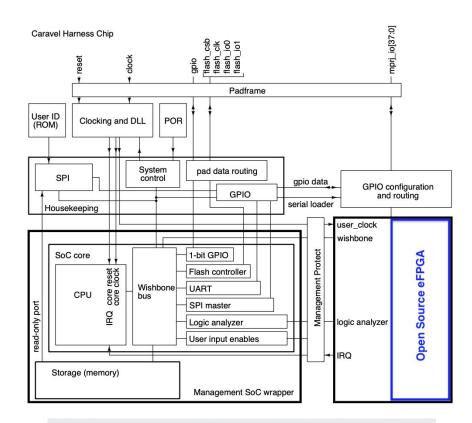

#### **ASIC Fabrication**

Caravel Harness:

- Microcontroller (PicoRV32)

- Logic Analyser

- I/O Pads

**CLEAR - The Open Source FPGA ASIC**

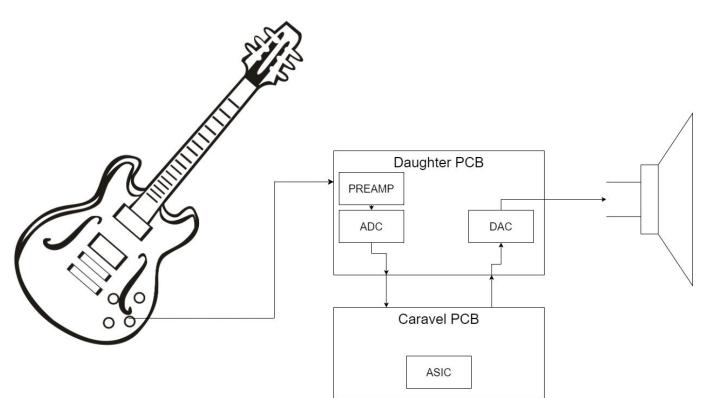

## Top Level Basic Design

- Allow for creation of pedal with inputs using the caravel PCB.

- A finalized design could potentially be added to the guitar itself rather than an individual pedal.

#### **Current Pedalboards**

- Current pedalboards use multiple effects requires multiple pedals connected in series.

- Our design will reduce multiple of these pedals down to one.

#### Requirements

- 3 types of effects

- Delay

- Reverb

- $\circ$  Compression

- Delay and reverb will each have two analog inputs

- Delay

- Magnitude

- Compression will have two analog inputs

- Threshold

- Ratio

- Audio Sample Size

- **16 bits**

- Sampling rate

- **10 kHz**

0

### **Engineering Standards**

- Audio in/out: Cable is a 2.1 mm DC input at 9 volts, with the center contact carrying the negative and the outer contact carrying the positive part of the current (Boss Standard).

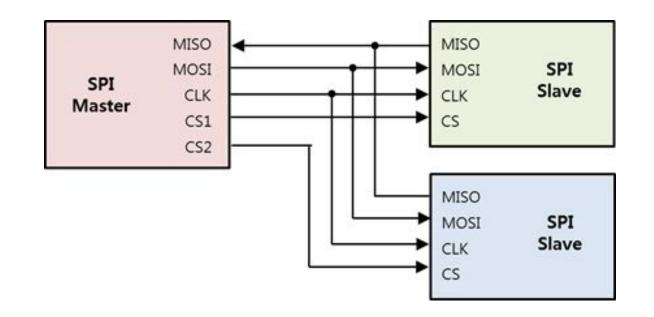

- SPI (Serial Peripheral Interface) for connecting ASIC to ADC, DAC, and SRAM

- IEEE 1364-2005 IEEE Standard Verilog Hardware Description Language

- ISO/IEC 9899:2018 C programming language (C17)

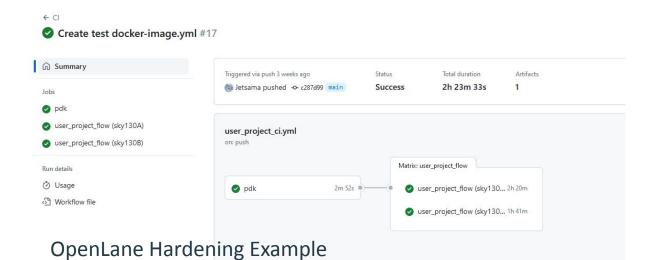

## Setup workspace

Created GitHub repository with wiki, issues, and milestones

Setup CI/CD for top level and module level testing

**Organization**

**Repository**

<u>WIKI</u>

| ASIC-GuitarPedal                                   |                                                                                   | 🖍 Edit Pins + 💿 Unwatch            |

|----------------------------------------------------|-----------------------------------------------------------------------------------|------------------------------------|

| P main - P 2 branches                              | ♥ 0 tags                                                                          | Go to file Add file * Code         |

| Your main branch is<br>Protect this branch from fo | isn't protected<br>force pushing or deletion, or require status checks before mer | Protect this branch X              |

| 🔋 Jetsama Merge pull reque:                        | est #12 from sdmay24-21/Python                                                    | × 78cfeze 3 weeks ago 🗿 34 commits |

| github/wo <mark>rkflo</mark> ws                    | Docker image run                                                                  | 3 weeks ago                        |

| vscode                                             | Impulse Audio Testing                                                             | last month                         |

| bin                                                | Trying new docker task                                                            | 3 weeks ago                        |

| def                                                | Initial commit                                                                    | 3 months ago                       |

| docs                                               | dpi change                                                                        | 2 months ago                       |

| gds                                                | Initial commit                                                                    | 3 months ago                       |

| lef                                                | Initial commit                                                                    | 3 months ago                       |

| <b>i</b> b                                         | Initial commit                                                                    | 3 months age                       |

| lvs/user_project_wrapper                           | Initial commit                                                                    | 3 months age                       |

| mag                                                | Initial commit                                                                    | 3 months ago                       |

| maglef                                             | Initial commit                                                                    | 3 months ag                        |

| openiane                                           | Remove termp readme                                                               | 2 months ag                        |

| python                                             | Merge branch 'main' into Python                                                   | 3 weeks ag                         |

| sdc                                                | Initial commit                                                                    | 3 months ag                        |

| signoff                                            | Remove termp readme                                                               | 2 months ag                        |

| spef                                               | Initial commit                                                                    | 3 months ag                        |

| spi/lvs                                            | Initial commit                                                                    | 3 months ag                        |

| verilog                                            | Start top level sim CPP code                                                      | 3 weeks ag                         |

| (*) .gitignore                                     | Git ignore and design info update                                                 | 2 months ag                        |

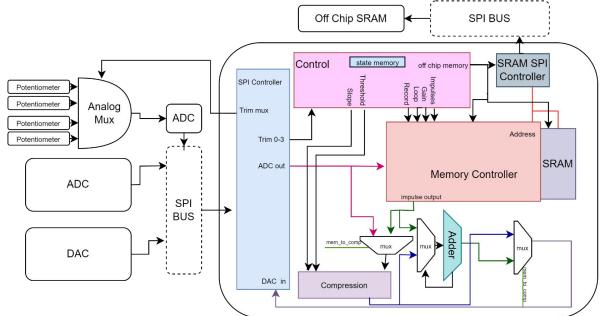

#### **Conceptual Final Design Diagram**

After deciding on bit width, clock speed, memory allocation, and protocols the following design was created.

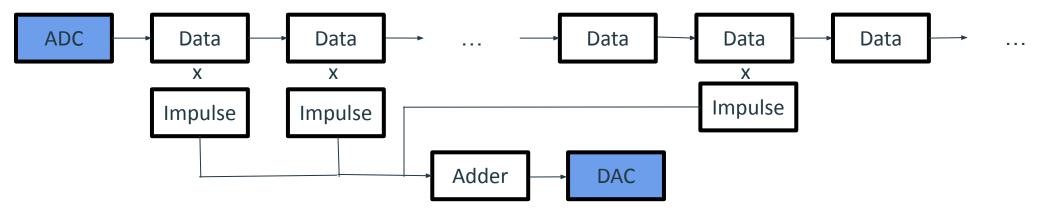

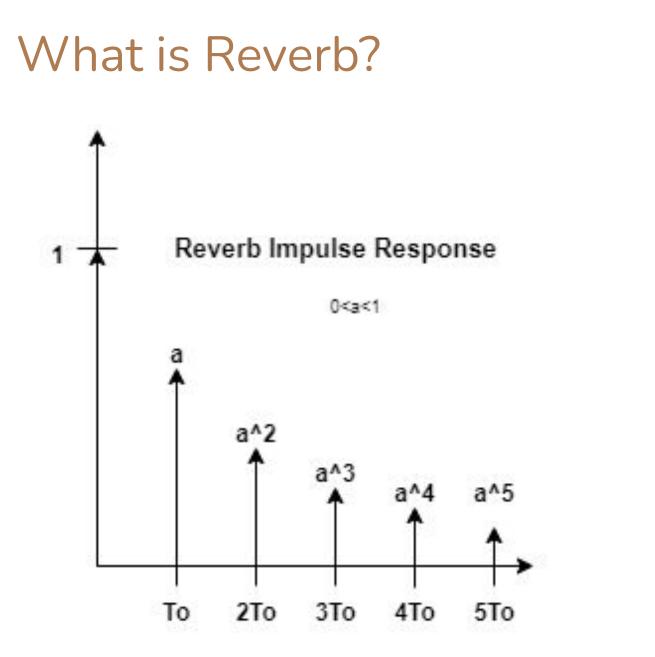

- Using a Finite Impulse Response implementation of many effects such as delay, reverb, or looping can be implemented

- For non linear effects the compression module has been added.

#### System Design-Control

We will be using the microcontroller, PicoRV32, as well as logic analyzer provided in the caravel harness

This allows to be <u>programmed</u> and revised via the SRAM

Will be used for Reverb and Delay functions and used to control compression module usage

More information can be found in the wiki: <a href="https://github.com/sdmay24-21/ASIC-GuitarPedal/wiki/Modules\_Control\_Module">https://github.com/sdmay24-21/ASIC-GuitarPedal/wiki/Modules\_Control\_Module</a>

#### System Design - Memory

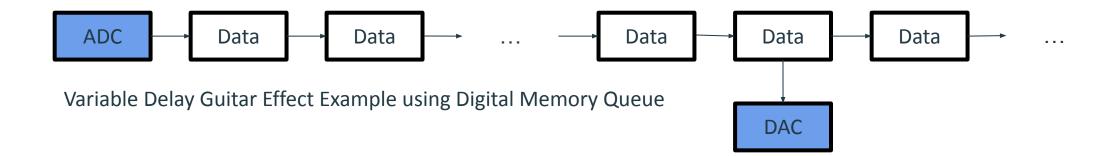

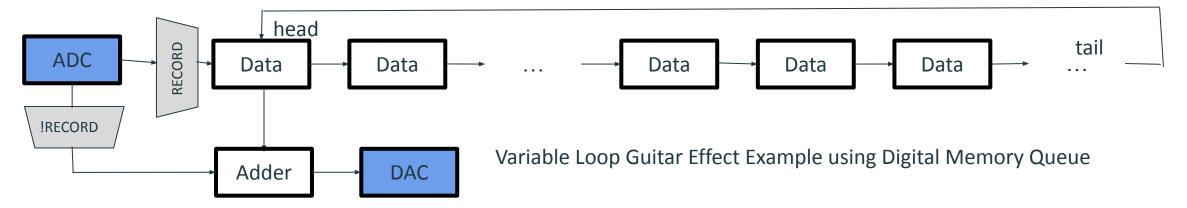

The memory is organized in a queue format with 16 bit values.

Every ADC Clock Cycle the data is added to the queue and the address is increased.

Depending on the mode, when memory runs out it will overwrite old data.

#### Other Pedal Effects using Queue Memory

Variable Impulse Response (Reverb) Guitar Effect Example using Digital Memory Queue

#### System Design-SPI

- Used to interface between memory on and off chip

- it allows for simultaneous data transmission and reception

- It is a synchronous device so the off chip components that it communicates to need to be on the same clock

Equally Spaced Delays with a scaling factor for each delay

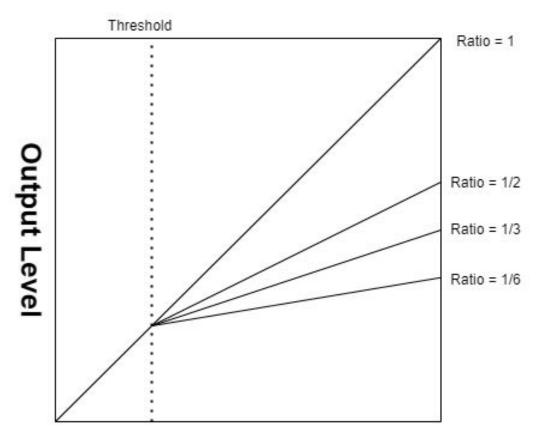

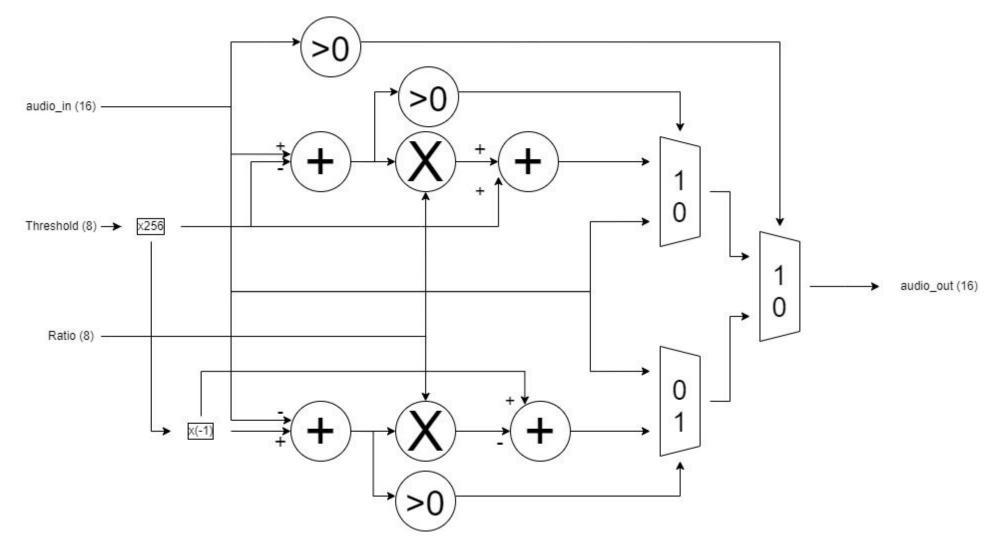

## System Design-Compression

- What is Compression?

- Inputs

- $\circ$  audio(16)

- threshold(8)

- ratio(8)

- When input is less than threshold, output

= input

- Otherwise, a portion of the input is added beyond the threshold

Input Level

#### System Design-Compression

## System Design-Compression

- Prototype Results

- The test results match the signal flow diagram

| Wave - Default :                           | 20        |          |             |             |           |          |          |                |        |              |        |          |

|--------------------------------------------|-----------|----------|-------------|-------------|-----------|----------|----------|----------------|--------|--------------|--------|----------|

| i •                                        | Msgs      |          |             |             |           |          |          |                |        |              |        |          |

| ✓ /compression_tb/threshold                | -No Data- | (00      | 9a          | cc          | aa        | 65       | ‡ f0     | aa             | 81     | ∦ff          | 55     |          |

| ✓ /compression_tb/ratio                    | -No Data- | (00)     | <b>↓</b> f0 | <b>Å</b> 3f | (c0       | 18       | (cc      | 55             | 101    | , ff         | laa    | (        |

| 🐓 /compression_tb/audio_in                 | -No Data- | (0000    | 5555        | 2aaa        | (f0aa     | , OfOf   | Ccf0     | \$5555         | (ff00  | 100ff        | CCCC   | <u>i</u> |

| 🐓 /compression_tb/audio_out                | -No Data- | (0000    | 5555        | le34b       | (0a00     | ÖfÖf     | ļda90    | 5555           | ļ ff00 | 100fd        | CCCC   | í –      |

| 🐓 /compression_tb/threshold16pos           | -No Data- | (0000    | 9a00        | cc00        | l aa00    | 6500     | ‡ f000   | l aa00         | 8100   | ļ ff00       | 5500   | l i      |

| /compression_tb/threshold16neg             | -No Data- | (0000    | 6600        | 3400        | 5600      | , 9b00   | 1000     | <b>\$</b> 5600 | 7f00   | 0100         | ab00   | l l      |

| 🐓 /compression_tb/audio_excesspos          | -No Data- | (0000    | bb55        | 15eaa       | 46aa      | aa0f     | ¦ dcf0   | ab55           | 7e00   | 101ff        | 77cc   | í –      |

| /compression_tb/audio_excessneg            | -No Data- | (0000    | 10ab        | 0956        | 6556      | 8bf1     | 4310     | , 00ab         | 8000   | <b>10001</b> | de34   | l i      |

| /compression_tb/audio_excessPosTimeRatio23 | -No Data- | 000000   | af9fb0      | 174bd6      | 34ff80    | 0ff168   | ¦ b00f40 | 38e339         | 007e00 | 01fd01       | 4f8d78 | í.       |

| /compression_tb/audio_excessNegTimeRatio23 | -No Data- | (000000) | 0fa050      | 024c2a      | 4c0080    | 0d1e98   | 3570c0   | 0038c7         | 008000 | ‡0000ff      | 938e88 | ĺ.       |

| /compression_tb/audio_excessPosTimeRatio15 | -No Data- | (0000    | af9f        | 174b        | 34ff      | 10ff1    | ₿b00f    | 38e3           | 007e   | 01fd         | 4f8d   | Ĩ.       |

| /compression_tb/audio_excessNegTimeRatio15 | -No Data- | (0000    | 0fa0        | 024c        | 4c00      | 0d1e     | 3570     | 0038           | 10080  | 10000        | 1938e  | <u>(</u> |

| 🐓 /compression_tb/audio_outpos             | -No Data- | (0000    | 5555        | le34b       | , deff    | OfOf     | ¢ ccf0   | 5555           | 817e   | 100fd        | a48d   | í.       |

| /compression_tb/audio_outneg               | -No Data- | (0000    | 5660        | 31b4        | 0a00      | OfOf     | da90     | 55c8           | , ff00 | 0100         | cccc   | 1        |

|                                            |           |          |             |             |           |          |          |                |        |              |        |          |

|                                            |           |          |             |             |           |          |          |                |        |              |        |          |

| ≅ ⊛ Now                                    | 100000 ps | ps ' '   | E E D E E E | 20000 ps    | 1 1 1 1 1 | 40000 ps |          | 60000 ps       |        | 80000 ps     | 1000   | 000 ps   |

| 🖌 😑 Cursor 1                               | 100001 ps |          |             |             |           |          |          |                |        |              | 1000   | 001 ps   |

| SI.                                        | 51 12     |          |             |             |           |          |          |                |        |              |        |          |

| mpression.v 🗙 h compression_tb.v 🛪 📰 Wave  | ×         |          |             |             |           |          |          |                |        |              |        |          |

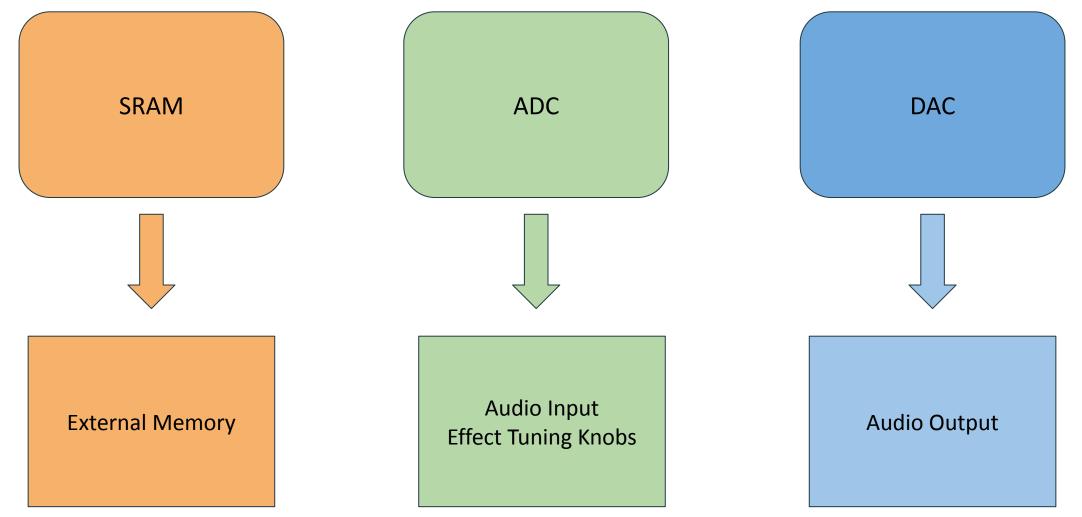

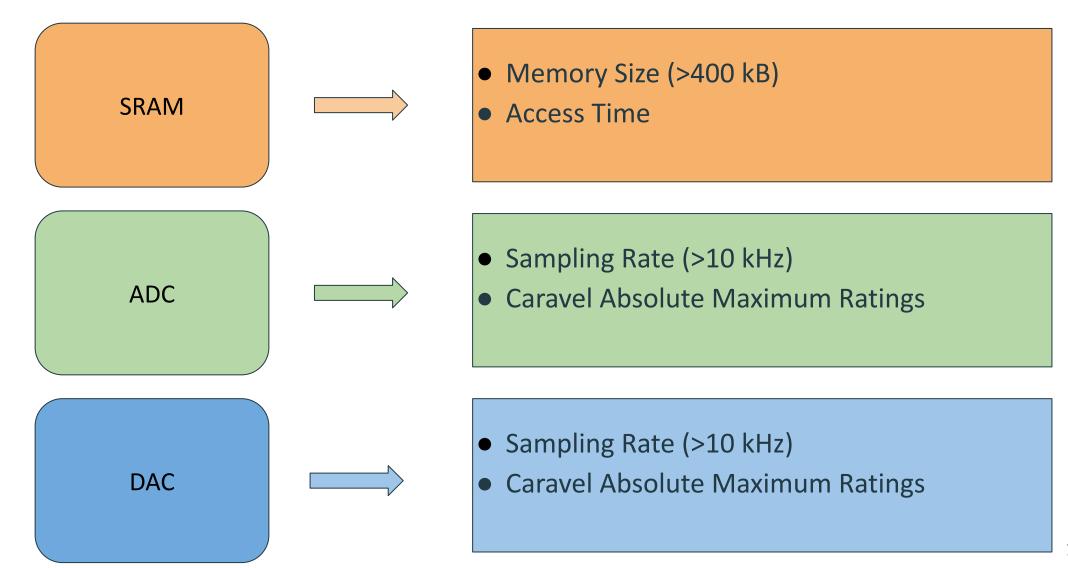

#### **Off-Chip Components**

#### **Selection Criteria**

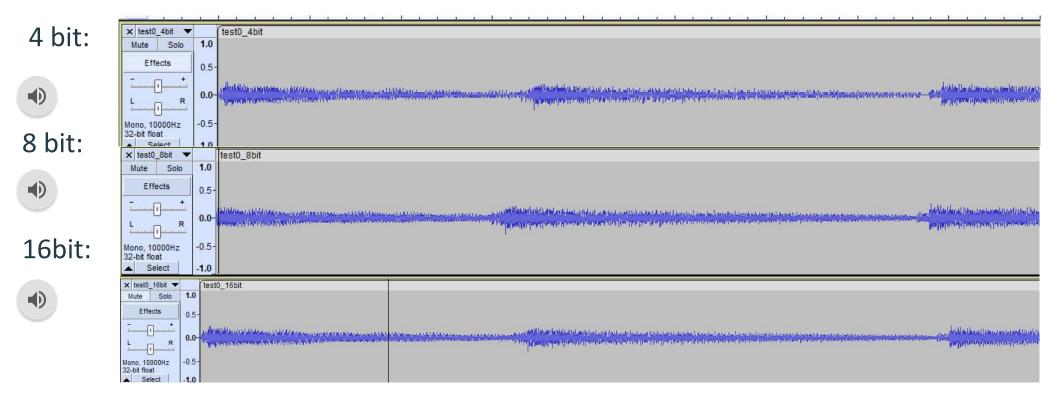

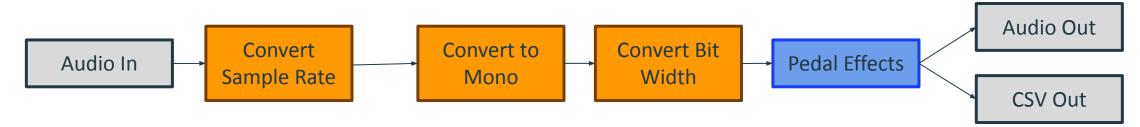

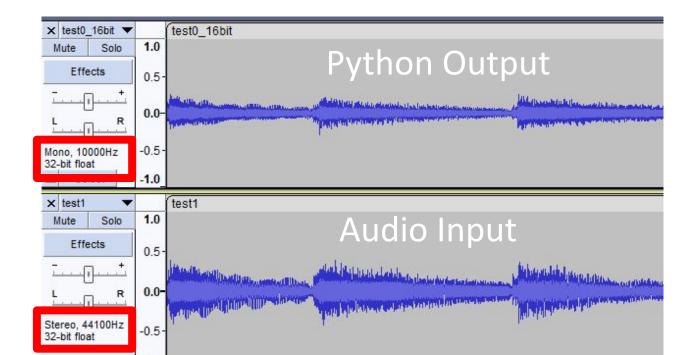

## Prototyping - Using Python

Python Module shows current implementation of verilog design.

Reflects the sampling rate change and bit width of design.

#### Python Module Steps

This process let us determine acceptable audio bit width and sample rates.

## Design Complexity

- What made your design hard?

- $\circ~$  keeping track of multiple clocks and managing on chip and off chip memory

- What kind of design iterations were needed?

- $\circ$  Initially our design was over simplified only having the function blocks in verilog

- We then decided that off chip memory was needed to support more storage if we wanted to record a reasonable length of audio, no previous group has had off chip components

- Layout space

- Keeping track of clock speeds to determine cycles needed for certain operations such as accessing memory, which is determined based on the SPI

## Project Schedule

| Digital ASIC Fabrication | Status        | October |    |    | October |   |    |    | November |          |   | December |    |    | February |   |    |    | March |   |    |    | April |   |    |    | Мау |   |    |

|--------------------------|---------------|---------|----|----|---------|---|----|----|----------|----------|---|----------|----|----|----------|---|----|----|-------|---|----|----|-------|---|----|----|-----|---|----|

| Task name                | 1             | 6       | 13 | 20 | 27      | 3 | 10 | 17 | 24       | 1        | 8 | 15       | 19 | 26 | 2        | 9 | 16 | 23 | 29    | 8 | 15 | 22 | 29    | 5 | 12 | 19 | 26  | 3 | 10 |

| Project Setu             | ıp            |         |    |    |         |   |    |    |          |          |   |          |    |    |          |   |    |    |       |   |    |    |       |   |    |    |     |   |    |

| Define Project Direction | Done 👻        |         |    |    |         |   |    |    |          |          |   |          |    |    |          |   |    |    |       |   |    |    |       |   |    |    |     |   |    |

| Define Project Scope     | Done 👻        |         |    |    |         |   |    |    |          |          |   |          |    |    |          |   |    |    |       |   |    |    |       |   |    |    |     |   |    |

| Research Resources       | Done 🔻        |         |    |    |         |   |    |    |          |          |   |          |    |    |          |   |    |    |       |   |    |    |       |   |    |    |     |   |    |

| Setup Workspace          | Done 👻        |         |    |    |         |   |    |    |          |          |   |          |    |    |          |   |    |    |       |   |    |    |       |   |    |    |     |   |    |

| Design                   |               |         |    |    |         |   |    |    |          |          |   |          |    |    |          |   |    |    |       |   |    |    |       |   |    |    |     |   |    |

| Top Level Design         | Done 🔻        |         |    |    |         |   |    |    |          |          |   |          |    |    |          |   |    |    |       |   |    |    |       |   |    |    |     |   |    |

| Individual Module Design | Done 🔻        |         |    |    |         |   |    |    |          |          |   |          |    |    |          |   |    |    |       |   |    |    |       |   |    |    |     |   |    |

| Off-Chip Components      | Done 🔻        |         |    |    |         |   |    |    |          |          |   |          |    |    |          |   |    |    |       |   |    |    |       |   |    |    |     |   |    |

| Design Verification      | In Progress 🔻 |         |    |    |         |   |    |    |          | <u> </u> |   |          |    |    |          |   |    |    |       |   |    |    |       |   |    |    |     |   |    |

| Block Testing            | In Progress 🔻 |         |    |    |         |   |    |    |          |          |   |          |    |    |          |   |    |    |       |   |    |    |       |   |    |    |     |   |    |

| Implementat              | ion           |         |    |    |         |   |    |    |          |          |   |          |    |    |          |   |    |    |       |   |    |    |       |   |    |    |     |   |    |

| Module Assembly          | -             |         |    |    |         |   |    |    |          |          |   |          |    |    |          |   |    |    |       |   |    |    |       |   |    |    |     |   |    |

| System Testing           | -             |         |    |    |         |   |    |    |          |          |   |          |    |    |          |   |    |    |       |   |    |    |       |   |    |    |     |   |    |

| PCB Design               | -             |         |    |    |         |   |    |    |          |          |   |          |    |    |          |   |    |    |       |   |    |    |       |   |    |    |     |   |    |

| Design Hardening         | -             |         |    |    |         |   |    |    |          |          |   |          |    |    |          |   |    |    |       |   |    |    |       |   |    |    |     |   |    |

| Precheck Verification    | -             |         |    |    |         |   |    |    |          |          |   |          |    |    |          |   |    |    |       |   |    |    |       |   |    |    |     |   |    |

| Finalizatio              | n             |         |    |    |         |   |    |    |          |          |   |          |    |    |          |   |    |    |       |   |    |    |       |   |    |    |     |   |    |

| Efabless Submission      | ~             |         |    |    |         |   |    |    |          |          |   |          |    |    |          |   |    |    |       |   |    |    |       |   |    |    |     |   |    |

| Bring-up Plan            | -             |         |    |    |         |   |    |    |          |          |   |          |    |    |          |   |    |    |       |   |    |    |       |   |    |    |     |   |    |

| Final Documentation      | -             |         |    |    |         |   |    |    |          |          |   |          |    |    |          |   |    |    |       |   |    |    |       |   |    |    |     |   |    |

| Final Presentation       | -             |         |    |    |         |   |    |    |          |          |   |          |    |    |          |   |    |    |       |   |    |    |       |   |    |    |     |   |    |

### Project Plan

#### Jonathan Hess

- Python and Verilator Testing

- Top Level Design

- Establish usage of EFabless tools

#### Samuel Heikens

- Compression Module

- PCB Design

# Yu Wei TanOff-Chip DesignPCB Design

## Python Module Testing

ł.

Python Module has been created which can:

- Simulate expected outputs

- Create test data for all 3 levels of top level verilog testing

- Create audio from module outputs

- Create audio from ASIC verilog output

Useful for hearing results of design before fabrication

## Verilog Top Level Testing

Using Verilator script along with python test data, testing will be done on 3 top level testbenches:

- 1 Without Control or SPI

- 2 Without SPI

- 3 Fully controlled by SPI

These will allow for verification that the verilog matches the python module. Also helps us with debugging to see which component is at fault

## **PCB** Level Testing

Create PCB using Kicad

Then create test plan for future students to do the following:

- Use soldering instructions to place parts

- Check connections with multimeter

- Use python code with <u>Caravel PCB</u>

- Use python script for loading and testing individual components

Caravel Test Socket PCB

#### **GitHub Runners**

#### Verilator Runner

• Runs Verilator Testbench on changed files if exists

#### **OpenLane Runner**

• Runs OpenLane Hardening on design

#### Conclusion

**Project Status**

• Modules are design and need to be tested using python script

Next Project Steps

- Create PCB test plan to check connections with test points

- Python script for loading and testing individual components

#### References

https://efabless.com/open\_shuttle\_program

# Q & A